- Technical Paper

- Hardware-In-the-Loop (HIL)

- Power Electronics

Resource Center

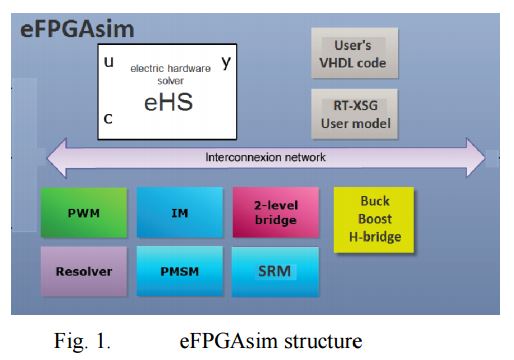

This paper presents an FPGA test system composed of an Induction Machine (IM), configurable as a Doubly-Fed Induction Machine (DFIM) or squirrel-cage induction machine, along with power electronic models suitable for virtual motor drive control development. The IM model is designed so that all parameters can be modified online. The power electronic part is customizable using a variable topology FPGA solver called Electric Hardware Solver (eHS). The system is designed for fast design iteration process by allowing circuit and parameter modification with a unique bitstream. The system allows control engineers to validate production controllers in real-time using a virtual IM.