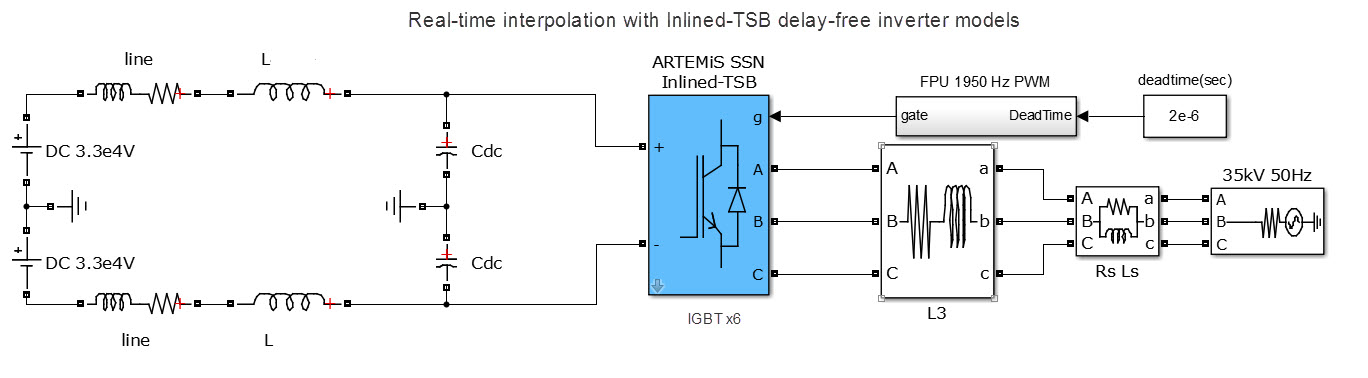

SSN simulation of VSC-HVDC with Inlined Voltage Inverter Compensation (IVIC)

The circuit shows the capability of ARTEMiS-SSN to accurately simulate 2-level Voltage Source Converter (VSC)-HVDC circuits

ARTEMiS-SSN incorporates a novel interpolation algorithm for 2-level inverters very similar to averaging inverter model with interpolation (also called Time-Stamped Bridge -TSB).

The main difference between this model and TSB is that there is NO DECOUPLING DELAY between the inverter and the rest of the circuit.

In some circuit like VSC-HVDC, a delay-free solution is mandatory to obtain an accurate simulation at relatively large time step. Also, not only the 'Inlined TSB' compensates for the output voltage, it also does compensate the bridge input current, a critical aspect in this demo.

In this demo, the sample is 20us, PWM frequency is 1950 Hz and a dead-time of 2 us is applied to the PWM firing.

Simulation shows that current and voltage amplitudes have a negligible jitter.

This course offers a diverse blend of essential background knowledge designed to equip you with the skills needed for any project related to communication protocols and/or Linux.

This course was originally built to provide background knowledge for the OPAL-RT and EXata co-simulation setup, but since then, it has been improved to yield a bigger reach.

You will learn more about the following:

– Shell Terminal, SSH and MobaXterm

– Linux, and the history of Linux at OPAL-RT

– Analyzing network protocols using TShark and Wireshark

– Understanding better the fundamental concepts of networks

– and more!

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course introduces OPAL-RT systems and applications using RT-LAB. This course is a prerequisite for eMEGASIM, eFPGASIM, and ePHASORSIM. RT-LAB is used in a variety of domains, including power systems, power electronics, automotive applications, aerospace, mechatronics and more.

Prerequisites:

• Basic knowledge of Matlab®/Simulink®

GOALS:

– Learn the fundamentals of real-time simulation

– Get started with RT-LAB Software

– Understand when and how to use distributed and parallel real-time simulation

– Connect models with I/Os

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course teaches the basics of the HYPERSIM® real-time simulation software platform and its operating principles.

GOALS:

– Understand the operating principles of HYPERSIM®

– Use ScopeView to analyze results

– Build and run a number of control and power system simulation cases showing the capabilities of HYPERSIM®

– Connect models with I/Os

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course covers the configuration of a real-time system using the OPAL-RT Power Electronics Add-On for NI VeriStand on the National Instruments hardware platform.

– Learn the fundamentals of real-time simulation

– Review the basics of NI VeriStand and the NI hardware platforms

– Understand FPGA-based simulation of power electronics using the eHS solver

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course is intended for new ePHASORsim users who want to learn Phasor Domain real-time simulation. ePHASORsim simulates electro-mechanical transient stability phenomena of very large power grids with thousands of buses, generators, transformers, transmission lines, loads and controllers.

Prerequisites:

• OP-101: RT-LAB – Real-Time Simulation Systems Fundamentals

GOALS:

– Understand the concept of Phasor Domain simulation features, benefits and limitations

– Import PSS/E, DIgSILENT or other model-based design tools into ePHASORsim

– Connect I/Os and communication buses with ePHASORsim

– Learn about the interaction of ePHASORsim and RT-LAB

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course is intended for power electronics and control engineers who want to perform fast power electronics real-time simulation using the combined power of FPGA and OPAL-RT’s unique dedicated solver eHS.

Prerequisites:

• OP-101: RT-LAB – Real-Time Simulation Systems Fundamentals

GOALS:

– Discover the features, flexibility and limitations of FPGA for power electronics real-time simulation

– Understand the overall architecture of real-time simulator between processors and FPGA

– Experience first-hand power electronics real-time FPGA applications using eHS solver

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course is intended for professionals who want to simulate power systems with ARTEMiS by converting their Simulink‘s SimPowerSystems™ based model into a complete HIL system.

Prerequisites:

• OP-101: RT-LAB – Real-Time Simulation Systems Fundamentals

GOALS:

– Learn how to run power systems models in real-time for HIL applications

– Take advantage of dedicated toolboxes for real-time simulation of power systems and power electronics

– Understand Artemis-SSN, State-Space Nodal solver, as well as its applications

– Learn how to improve the real-time simulation switching results with RT-EVENTS

– Learn how to adapt your SimPowerSystems model for real-time simulation

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course is intended for professionals who want to simulate power electronic circuits with our FPGA-based solver: eHS. This toolbox provides the flexibility and speed required for very fast power conversion applications for HIL simulation.

Prerequisites :

• OP-101 : RT-LAB – Real-Time Simulation Systems Fundamentals

GOALS:

– Learn how to run power electronic circuits in real-time for HIL applications

– Take advantage of FPGA high performance for solving power electronic circuits in real-time

– Learn how to design your power electronic circuits with the OPAL-RT Schematic Editor

– Learn how to implement a control algorithm on CPU for your power electronic circuits

– Learn how to interface your power electronic circuits design with external controller

– Learn how to simulate faults on power electronic converter circuits

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course is intended for new ePHASORSIM users who want to learn Phasor Domain real-time simulation. ePHASORSIM simulates electro-mechanical transient stability phenomena of very large power grids with thousands of buses, generators, transformers, transmission lines, loads and controllers.

Prerequisites:

• OP101: RT-LAB – Real-Time Simulation Systems Fundamentals

GOALS:

– Understand the concept of Phasor Domain simulation features, benefits and limitations

– Import PSS/E, DIgSILENT or other model-based design tools into ePHASORSIM

– Connect I/Os and communication buses with ePHASORSIM

– Learn about the interaction of ePHASORsim and RT-LAB

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course covers how to use the FPGA-Based electric hardware solver (eHS) on the Power Electronics Add-On for NI VeriStand, developed by OPAL-RT, with NI’s VeriStand software to give a user the tools necessary to test power electronics and electric motors in real-time.

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

This course covers the cyber-physical co-simulation setup between Keysight’s EXata CPS and OPAL-RT’s RT-LAB / HYPERSIM. Learn how to install EXata CPS on your computer, license the software, and go through step-by-step examples on how to implement faults, cyber attacks and integrate both software.

GOALS:

– Learn how to install and configure the EXata CPS software

– Go through different step-by-steps showing how to couple the two software

– Implement your first cyber-attacks and analyze the impacts

– Connect an external device to your co-simulation setup

Note: All self-paced e-Learning courses are available for free for OPAL-RT customers.

Dr. Ron Brandl completed his studies in electrical engineering in 2010 and received his doctorate in engineering from the University of Kassel in 2018. Since 2011, Ron Brandl is working as a research associate at the Fraunhofer Institute for Energy Economics and Energy System Technology – IEE, where he heads the group ‘Power Electronics Applications’ and is part of the Fraunhofer Competence Center ‘Cognitive Energy Systems’. Additionally, Ron Brandl is working as project manager and researcher at the European Distributed Energy Resource Laboratories e.V. – DERlab since 2018. His expertise covers topics such as real-time simulations, power hardware-in-the-loop technology, power electronics and system stability, electromobility and AI in energy. He is involved in the design of test centers for smart grids, participates in various national and European research projects, is part of several working groups, such as the IEEE Task Force “Real-Time Simulation of Power and Energy Systems”, the IEEE P2004 Working Group “Recommended Practice for HIL Simulation Based Testing” and he is National Expert and Operating Agent of the IEA-ISGAN Annex 5 “Smart Grid International Research Facility Network”.

Danielle Sami Nasrallah received an Engineer’s diploma in electromechanical engineering and a Diplôme d’Études Approfondies in electrical engineering from École supérieure d’ingénieurs de Beyrouth (ÉSIB), Beirut, Lebanon in 2000 and 2002, respectively, and a Ph. D. degree in Robotics Modelling and Control from McGill University, Montreal, QC, Canada, in 2006. During her Ph. D. studies she worked on a part-time basis at Robotics Design as a control and robotics engineer. She moved to Meta Vision Systems in 2006-2007 as a control and applications engineer.

In 2008, she joined the electrical department of the Royal Military College of Kingston as an assistant professor and, in 2009, she was a visiting assistant professor at the American University of Beirut. From 2010 to 2014, she worked as a consultant in control and systems engineering. In 2014, she joined OPAL-RT TECHNOLOGIES where she is presently a technical lead in control and intelligent mobility. She retained links with academia as she lectures in Robotics and Control at both Concordia and McGill Universities.

Sebastian Hubschneider finished his studies of electrical engineering and information technology at the Karlsruhe Institute of Technology (KIT) in June 2015 with the academic degree Master of Science. During his time at the University, he specialized in power engineering with a focus on energy grids and the energy sector in general, including markets and the economy.

Since July 2015, Sebastian works as a research associate at the Institute of Electric Energy Systems and High-Voltage Technology (IEH), KIT. His research focuses on Power Hardware-in-the-Loop systems in conjunction with energy grids and electrical equipment.

The development process of the microgrid controller (MGC) is that we first develop the controlling function in C that matches with the SIL preliminary algorithm developed by OPAL-RT/HYPERSIM. Secondly, a real HIL lightweight IED controller based on an iec61850 library is developed. Thirdly, we then test both the developed algorithm and the lightweight IED controller via various simulation scenarios. We perform testing scenarios of a developed MGS in a microgrid cyber-physical simulation subject to cyber-attacks in our lab. These testing are designed through performing two MGC testing scenarios. First, a delay attack is implemented, when the microgrid is islanded–the MGC monitors whole MG circuit breakers (CBs) specifically in this scenario—and the PCC CB should disconnect Load 4. Secondly, we test a packet manipulation on a measured data attack. External MGC HIL monitors the power generation as well as load consumption, in case (no balance) a trip command is issued to disconnect Load 3 via GOOSE. We then provide this development procedure for HIL MGC, which can communicate with the real-time simulator’s HYPERSIM simulation model over IEC 61850 GOOSE, as well as run the designed intelligent controlling algorithm and send the dispatching signal back to the real-time simulator model.

Georg Lauss received the Dipl.-Ing. degree from the Johannes Kepler University JKU Linz, Austria, in 2006 and jointly from the Eidgenössischen Technischen Hochschule ETHZ, Zürich, Switzerland, and the Université Pierre-et-Marie-Curie, Paris, France. He is a researcher with the AIT Austrian Institute of Technology, Vienna, Austria. His main interests include electromagnetic systems, power electronics, system and control theory, mathematical methods for optimized control systems, hardware-in-the-loop simulation systems, and real-time simulation for electromagnetic power systems.

Georg Lauss is the Chairman of the IEEE WG P2004 Recommended Practice for Hardware-in-the-Loop (HIL) Simulation Based Testing of Electric Power Apparatus and Controls and the IEEE PES Task Force on Real-Time Simulation of Power and Energy Systems.

Charalambos Konstantinou is an Assistant Professor of Computer Science (CS) and Affiliate Professor of Electrical and Computer Engineering (ECE) at the Computer, Electrical and Mathematical Sciences and Engineering Division (CEMSE) of King Abdullah University of Science and Technology (KAUST), Thuwal, Saudi Arabia. He is the Principal Investigator of the Secure Next Generation Resilient Systems Lab (SENTRY) and a member of the Resilient Computing and Cybersecurity Center (RC3) at KAUST. His research interests are in secure, trustworthy, and resilient cyber-physical and embedded IoT systems. He is also interested in critical infrastructures security and resilience with a special focus on smart grid technologies, renewable energy integration, and real-time simulation.

He received a Ph.D. in Electrical Engineering from New York University (NYU), NY, in 2018, and a Dipl.-Ing.-M.Eng. Degree in Electrical and Computer Engineering from National Technical University of Athens (NTUA), Greece, in 2012. Before joining KAUST, he was an Assistant Professor with the Center for Advanced Power Systems (CAPS) at Florida State University (FSU). He is a Senior Member of IEEE, a member of ACM, and an ACM Distinguished Speaker (2021-2024).

Christine Van Slyke is Vice President of Global Sales and Marketing at SCALABLE Network Technologies. She has been with SCALABLE for over seven years and has a Masters in Business Administration. She has more than 20 years of experience in business, technology, and strategy development. Prior to SCALABLE, she spent more than a decade helping TELUS—one of Canada’s leading telecommunications and managed solutions providers expand its offerings across the Province of Ontario.

This talk will discuss methods to implement different topologies of DC Microgrids.

CENER has developed an EMS to manage either microgrids or renewable generation plants hybridized with energy storage systems. Its first prototype has been validated at its facilities in the ATENEA microgrid, which have been previously simulated through RT-LAB using a OP4510 target.

The EMS consists of a SCADA where the user can configure almost any plant based on renewable generation systems, loads, electric vehicle, connection to utility grid, gen-set and different types of energy storage systems. Also, the EMS lets the user select between several strategies and plant control depending on the configuration chosen before and their interests.

Since the study focuses on the ATENEA microgrid, which is composed of lithium, flow and lead-acid energy storage systems, a gen-set, programmable loads, one electric car, solar generation and grid connection, this system has been modelled and then simulated in an OPAL-RT target.

Through a previous process of validation of every model as well as the communication system with the EMS, the built system allows to design, adjust, and validate the strategies and control systems before testing them in ATENEA.

Synchrophasor measurement technology is based on calculation of phasors obtained from Phasor Measurement Units. This technology is used in several countries to get better observability of electric systems. CEPEL’s Synchronous Phase Measurement Laboratory (LabPMU), in Cidade Universitária, Rio de Janeiro, RJ, is a laboratory infrastructure conceived to provide performance tests of PMUs and research on applications based on this technology. One relevant project carried out at LabPMU is to use Fractional Cycle Digital Fourier Transform Algorithm for Phasor Measurement Units (FC-DFT). This project aims to achieve faster PMUs, regarding the increasing presence of power electronics interfaced resources in power system generation and transmission. The presentation will show power electronic electrical simulations using HYPERSIM, in order to show the benefits of the algorithm. Two different simulation circuits were used: an HVDC multi-infeed circuit, as that arrangement is extensively used in the world, especially in Brazil; and a simulation of a distribution circuit provided with a PV array connected to the distribution electrical system through a converter (switching function model). Some occurrences of the power electronics equipment are simulated, and the results are the input of the FC-PMU. The FC-DFT results are then analyzed, showing that the equipment may deliver beneficial information for the control system operator and for early forensic analysis.

Low-inertia power systems can experience high rates of change of frequency and large frequency deviations during power imbalances. Inertia emulation using high power density storage systems such as a Flywheel Energy Storage System (FESS), can help limit the rate of change of frequency following sudden changes in generation or demand. In this presentation, a new adaptive inertia emulation controller for a high-speed FESS is proposed. To validate the behavior of the FESS with the proposed control design, the controller is implemented on a real 60 kW high-speed FESS, using the concept of rapid control prototyping. The performance of the FESS, equipped with the adaptive inertia emulation controller, is evaluated by means of Power Hardware-in-the-Loop (PHIL) simulations using the real-time simulation model of a low voltage microgrid. To reduce the overall loop delay, the established PHIL setup uses fiber optic connections to the power amplifier and several I/O expansion units. The State-space Nodal (SSN) solver is also applied to reduce the simulation time step of the microgrid model. The results of PHIL simulation show that the FESS with the newly-proposed adaptive inertia emulation controller outperforms the previously-suggested adaptive control designs, in terms of reducing the maximum rate of change of frequency and limiting the maximum frequency deviation, while not demanding significantly more energy from the FESS.

Modular Multilevel Cascaded Converters (MMCC) have attracted considerable attention from the power electronic and drive research community since their introduction at the beginning of 2000. Originally, MMCCs were proposed for High-Voltage Direct Current (HVDC) transmission systems. Still, recently, they have been introduced into other fields, e.g., static compensators, wind energy conversion systems, and motor drives.

Among MMCCs, the Modular Multilevel Converter (M2C) is a well-established topology used extensively for HVDC transmission. However, the M2C has some difficulties in achieving good performance in applications where the electrical machine operates at a very low speed.

Therefore, other MMCC topologies, such as the Hexverter, the Modular Multilevel Matrix Converter, the Series-Shunt MMCC have been studied in the last few years. However, novel converters require complex implementations and control strategies that have hindered the number of works where experimental results of these topologies are reported.

In this context, this presentation introduces a joint project lead by the University of Santiago of Chile, in collaboration with OPAL-RT and Conecta Engineering, where a reconfigurable MMCC composed of 120 power modules is implemented using OPAL-RT MMCC modules. Thus, the testbed can perform rapid control prototyping testing and Power Hardware in The Loop analyses of novel topologies such as M3C, Hexverter and other novel topologies.

Smart grid applications, especially those focusing on the coordination of distributed flexibilities, include many devices governed by increasingly complex software architectures, all linked together by communication technology. In theory, some of these applications would have the potential to revolutionize the way the grid is being operated. However, in practice they are met with skepticism due to the uncertainties and vulnerabilities that these systems might introduce. Therefore, exhaustive testing and validation steps need to be undertaken before deployment to guarantee reliability. Approaching this task manually is extremely time-consuming and error prone. In this presentation we show an approach to automatically generate cyber-physical test beds which allow the evaluation of such applications. The proposed method uses PSAL (Power System Automation Language) to describe the cyber-physical system under test, i.e., the electrical network, the sensors, the actuators, as well as the various controllers/software components and their interconnections. Several model generators parse the PSAL code, and they automatically build a real-time simulation of the physical system; they establish various interfaces for the controllers to interact with the sensors and actuators; they package the controllers and deploy them to their designated locations; and they configure the data collection framework to enable the recording and analysis of experiment data.

The success of EVs depends on the charging infrastructure. Due to different charging standards, it is difficult for EV manufacturers to rely on any one standard. Therefore, there is a need to design a charging system which can fit in many charging protocols. This presentation will give an insight into the different charging standards and their probable solutions.

This paper presents the design and development of a wind turbine emulator (WTE), based on a separately excited DC motor, using an OPAL-RT digital simulator. The power-motor speed characteristics for different armature voltages in the motor are like the power-turbine speed characteristics for varying wind speeds in the turbine. WTE is a power electronic step-down chopper that is interfaced with a mathematical model of wind turbine present in the RT simulator. The wind turbine model generates a reference armature current that is compared with the actual armature current of the motor. The PI controller is used here to minimize the current error and provides a desired switching pulse to the MOSFET. The laboratory setup consists of a WTE that is coupled to a three-phase permanent magnet synchronous generator (PMSG) as a standalone system. The turbine model and PMSG model are presented in this paper. The effectiveness of this RT-LAB-based WTE is verified by simulation and experimental results under various wind speed and load change conditions.

Precision is the most important aspect for designing, controlling, or validating any power system—and due to this, real-time simulation is growing. Especially in design, it allows accurate modeling of a system, which is the baseline of design. Therefore, in this work, a switching function-based model of a three-phase voltage source inverter is transformed into a real-time model using OPAL-RT’s real time simulator (OP4510) with hardware-in-the-loop technology for its implementation in an actual power system. For the validation of its behavior in real time, it has been compared to the detailed inverter model having the same input variables and control dynamics. The results reveal that the proposed inverter model keeps the total harmonic distortion within limits as per the latest grid code and, at the same time, it maintains the required accuracy for the system. Further, this work shows the importance of real-time simulation by comparing its mode of simulation with other offline modes of simulations such as normal, accelerator and rapid accelerator.

This work proposes an interfacing technique that uses the built-in three-phase transmission line models available in simulation platforms to perform Root Mean Square (RMS)-Electromagnetic Transient (EMT) real-time, multi-domain and multi-rate co-simulation. The main objective of this paper is to show the application of this kind of simulation in hardware-in-the-loop (HIL) testing of protective relays. Two well-known platforms are considered in this work: OPAL-RT with its ePHASORSIM tool is used for RMS simulation, and RTDS is used for EMT simulation. However, the proposed technique is sufficiently general to be applied to other real-time simulation platforms that have similar built-in transmission line models. To convert waveforms to phasors, a non-buffered rapid curve fitting method was implemented to attend to real-time constraints. During the testing phase of this research, tests for the HIL were completed using an actual transmission line protection relay. The presented results of tests highlight the benefits of the proposed interfacing technique.

With the increasing level of penetration of renewable production and the need for long-distance energy transport, Multi-Terminal DC grids (MTDC) have become a crucial field of research for the future development of wide-scale DC grids.

These MTDC grids pose several technical challenges: protecting the DC grid against electrical faults; transforming DC voltage; and controlling the flow of energy in a meshed system. The possible technical solutions and new technologies addressing these issues need to be assessed through real-time and HIL simulations to demonstrate the system’s performance.

With that perspective, an MTDC HIL test bench is being developed at the Supergrid Institute to test and validate any proposed control and protection solution.

On this HIL setup, several Raspberry PIs are used to simulate in real time the different IEDs of the system: protection relays, station supervisors, DC Grid Control. These IEDs communicate with each other and with the electrical model using the IEC61850 communication protocol.

The electrical benchmark is a 4 Terminal DC Grid, modelled with HYPERSIM and running in real time with an OP5700 simulator.

The HYPERSIM model uses a Graphical User Interface (GUI), coded in Python and using the Python API provided by HYPERSIM. This interface allows a user to interact with the electrical system: launch a start-up sequence to connect the DC Grid, simulate a fault to test the implemented protection strategy.

Part 1: The global power system’s transition to nearly 100% renewable-based generation presents new challenges not only in terms of control strategies but also in terms of tools required to perform HIL simulations. In this context, conventional generators such as synchronous machines may be gradually replaced by power electronic converters or similar generation units. HIL simulation setups of large grid models with multiple switching inverters are a challenge due to the high-level of accuracy required. The coupling of the power electronic domain with the network-level domain is currently the major issue to overcome. Two approaches are followed: the first one involves the coupling of the FPGA and the CPU model, while the second one uses the ARTEMiS library.

Part 2: Non-real-time or offline simulation methodologies using numerical solving techniques for network or component models have their limitations with respect to the necessity of high complexity. Therefore, they may prove insufficient with respect to resulting simulation accuracy or computation time. Real-time simulation based HIL simulation testing can overcome these issues, because physical hardware equipment, including the entire control system, is interlinked with the simulated network model via HIL interfaces. This enables natural coupling which guarantees the conservation of instantaneous power via the conservation of the through and across quantities at interfaces as exists in the real-world system.

Georg Lauss received the Dipl.-Ing. degree from the Johannes Kepler University JKU Linz, Austria, in 2006 and jointly from the Eidgenössischen Technischen Hochschule ETHZ, Zürich, Switzerland, and the Université Pierre-et-Marie-Curie, Paris, France. He is a researcher with the AIT Austrian Institute of Technology, Vienna, Austria. His main interests include electromagnetic systems, power electronics, system and control theory, mathematical methods for optimized control systems, hardware-in-the-loop simulation systems, and real-time simulation for electromagnetic power systems. Georg Lauss is the Chairman of the IEEE WG P2004 Recommended Practice for Hardware-inthe-Loop (HIL) Simulation Based Testing of Electric Power Apparatus and Controls and the IEEE PES Task Force on Real-Time Simulation of Power and Energy Systems.

The distribution system has undergone tremendous upgrades that have leaned toward a more carbon-free, reliable, and resilient infrastructure. This has been made possible by incorporating more sophisticated controllers in conventional generation, smart inverters based distributed generation, automatic load regulators, seamless interfacing of mini, micro and nano grids etc. To the contrary, the system is exposed to different events resulting from intermittent generation, as well as the unpredictable and uncertain behavior of loads in distribution networks. Real-time digital simulators from OPAL-RT let the power professionals study these events through digital twin models and by tweaking system parameters to create diverse and disruptive steady, dynamic, and transient event signatures–and also provides real datasets through the direct interface of sensors, PMUs, remote terminal units, smart measurement/meters, for testing and validating the AI-centric data analytics. Online testing of data analytical tools is made easy through real-time simulators by OPAL-RT as it has dedicated input and output digital/analog channels for export/import signals from/to power system models and supports standard communication protocols such as DNP3, C31.118-2011, etc. This presentation revolves around the wide usage of OPAL-RT’s real-time digital simulations in prospective testing environments of data analytics through real and simulated distribution phasor measurement units. Actual case studies are emphasized in the presentation.

Wide Area Monitoring and Smart Automation (WAMSA) is today’s innovative research area under smart grid execution to overcome real-time protection difficulties. Modern communications and information processing technologies offer outstanding real-time benefits. The development of big data applications and satellite uplinks are rapidly changing. Several new measurement devices are being incorporated into an advanced smart grid metering infrastructure. In this process, PMUs can sense, converting signals from voltage and current into digital form under real-time wide-area monitoring systems. In modern power systems’ real-time applications point of view, big data analytics are playing a vital role with increasingly popular technological concept that contains smart electricity facilities, for instance, smart power control, energy utilization, and management. Initially, it emphasized smart grids, modern data analytics, massive-scale information control, and reliable monitoring methods with the extreme size of data required. This paper summarizes the PMU setup and installation overview in the Unified Real-time Dynamic State Measurement project (URTDSM) with the synchrophasor based wide-area monitoring system in India. The novelty of this presentation is to focus on big data potential functions and practices like fault detection, transient stability, load forecasting, and power quality monitoring into real-time wide-area monitoring.

The advancement of technology has allowed the exponential development of electric engineering applications, and several of these fields are: digital simulation in real-time in conjunction with synchro-phasor measurements in electrical power systems; the generation of data applying the Monte Carlo method; and the analysis of data by application of data mining techniques. Research on load-shedding schemes, together with the application of the above-mentioned fields, allows the prediction of certain events that have caused the disconnections of large amounts of load, and even the operating output (blackout) of large power systems, around the world.

The present project proposes a methodology for the implementation of a load shedding scheme as a function of voltage and frequency that allows, through an indicator, and by means of an indicator calculated in real time through a previously-trained regressor, to determine the amount of load to be disconnected after the occurrence of a contingency for loss of generation.

To do this, a comprehensive real-time digital simulation platform is implemented, which uses OPAL-RT’s ePHASORsim, together with the functionalities of CENACE’s WAMS system, WAProtector, to execute a Software in the loop (SIL) to perform adaptive load shedding in real time, triggered when the indicator condition calculated by the regressor previously-trained with simulation results obtained from PowerFactory is met.

Our UPS HIL Testbench presentation will focus on how we used OPAL-RT’s solution in the UPS HIL system design to speed up the product launch, as well as key parameters Gs Understanding and TSB bridge usage in the UPS HIL system.

Japan intends on attaining carbon neutrality before 2050, and offshore wind farms are one of the primary energy sources that will help to realize this ambition. Since the sea depth around Japan is more that 50m, facilities of transmission systems for offshore wind farms must be installed on floating platforms. Middle frequency (500Hz) convertors are a promising equipment that reduce the weight and volume of transformers used for substations on the floating platform. MMC is a solution that can operate at 500Hz with less switching loss. It however requires much system analysis to develop and tune the control system. Real-time simulators are a useful tool for small academic laboratories to study on MMC. It saves risks of hardware trouble caused by mis-operation of the control system. An example of studies–such as the fundamental operations of scaled models (200V, 1A) of MMC convertors, real time simulation for tuning of control systems, as well as harmonics studies in our laboratory–will be introduced in the presentation

Sharing the user story / experience from Maschinenfabrik Reinhausen (MR) with OPAL-RT products in a Modular Multilevel Converter development project, problems, challenges and benefits.

This study presents an interface method (IM) to interconnect real-time simulators (RTSs) without amplifiers for different intelligent electronic devices (IEDs), such as protective relays, smart meters, and other devices. It is a significant topic for the power systems protection community because there are many protection devices with different requirements. These protection devices have pinouts that measure bus voltages/currents and breaker pole states and generate trip/close pulse signals. Most of the emulation test beds with RTSs and HIL need amplifiers to connect IEDs from different product manufacturers because the low-voltage interface levels are not available in some instruction manuals. Additionally, commercial amplifiers have cutoff frequency limitations and have an excessive cost when several IEDs are wired onto test beds. Then, the validation of protection and control systems with RTSs and IEDs in the loop from different vendors without amplifiers results in an unfeasible alternative. In this paper, the IM was based on using an interface box, power source, and RTS to identify IED inputs/outputs. The sequence to recognize IED pinouts and calculate the current/voltage scaling factors is described. The IM was validated satisfactorily with RTS and a protection device (with unknown pinouts) in the loop.

Emilio C. Piesciorovsky graduated with a BS in electrical engineering from the National Technological University, Argentina (1995). He received his MS in marketing international from La Plata National University, Argentina (2001). He worked as an engineer for Pirelli Power Cables and Systems, SDMO Industries, ABB, and Casco Systems.

He completed his MS (2009) and PhD (2015) in electrical engineering from Kansas State University. Then, he worked as a postdoc at Tennessee Technological University and Oak Ridge National Laboratory.

Currently, he is a professional technical staff member and lab space manager in the power system protection area at Oak Ridge National Laboratory. He is the author/coauthor of more than 20 publications, and is an IEEE senior member; piesciorovec@ornl.gov.

As the complexity of today’s power system increases, it is crucial to have a system protection training program that can incorporate evolving changes and mimics a realistic environment. Dominion Energy is developing real-time models to conduct closed-loop tests. The Substation Automated Training Simulator (SATS) infrastructure is composed of a OP5700 simulator, four OP5600 expansion boxes, and 24 Omicron Power Amplifiers, all mounted on five equipment panels. This system is hardwired to protective relay equipment panels and to primary equipment. There are a variety of use cases that can introduce various abnormal scenarios that may be encountered in a real power system. This closed-loop system enables a simulation to seamlessly replicate the power system response while switching primary substation equipment. Beyond that, it also provides a method of validating entire protection schemes including equipment wiring, individual protective relay settings, and overall device coordination.

Flavia Khatounian received her diploma in Electrical and Mechanical Engineering from Saint Joseph University of Beirut (USJ-ESIB), Lebanon, in 2002, and the Ph.D. degree in Electrical Engineering from the Ecole Normale Supérieure (ENS) de Cachan, France, in 2007. She joined the Saint Joseph University of Beirut in 2008 where she is nowadays a full-time associate professor at the Faculty of Engineering and Head of the Electrical and Mechanical Engineering Department.

Her research interests include power electronics and electrical machines identification and control. She serves as a reviewer for high impact factor journals and international conferences and is a member of the IEEE, IEEE Industrial Electronics Society (IES) and IEEE Robotics and Automation Society (RAS) where she volunteers currently as a vice chair of the Lebanon Joint Chapter, RA24/IM09/CS23 (CH08807). She is the author or coauthor of 2 book chapters and more than 40 scientific papers.

We are currently undergoing a major digital transformation in almost all processes of an electricity distribution company. CPFL (www.cpfl.com.br), one of the largest companies in the sector of energy in Brazil, seeks digitalization in all its operational processes, aiming at gains such as cost reduction and increase in the quality and productivity of services.

Oftentimes, technology is viewed mainly from the perspective of changes that it brings in the lives of people and especially in the ease that is occasioned in its application. Whilst not deviating from this traditional perspective, this Paper goes further to examine the role of real-time simulation in the development of Power Sector of developing economies, especially in Nigeria and the West African Region. The Paper attempts the contribution of Real-time solutions to the development of human capital development whilst at the same time taking a stock of the economic opportunity provided for manufacturers in their incursion into the African markets. It concludes by showing a possible win-win solution for all stakeholders in which the Power Sector records improvement through these technologies while manufacturers build on this business to increase turnover and undertakes researches into new areas.

The use of DC technology in various applications is increasingly coming to the fore with a view to efficient and sustainable energy supply with the integration of renewable energies and energy storage systems. Besides advantages in improved controllability, system efficiency, and economic feasibility, protection strategies of dc grids are more challenging compared to ac grids due to the missing natural zero crossing of the current. Therefore, specially designed dc circuit breakers or the conception of breaker-less dc grids, using current limiting modulation schemes need to be developed.

With the rapid growth of renewable and distributed energy resources (DER), their impact on the legacy AC grid is becoming an important topic. Among integration strategies, the dc microgrid is attractive because of the high efficiency and simple dc interface for various DERs and energy storage devices. When connected to the ac grid, it utilizes a dc-ac converter as the interface. However, there are still many major challenges to integrate dc microgrids in the legacy power system.

Today, the dc-ac converters lack rotational inertia and do not interact with the grid like the SMs.To solve these problems, dc-ac converters mimicking synchronous machinesare proposed. These virtual synchronous machines (VSM) offer several benefits.

This project proposes a microgrid integration concept to address above mentioned issues. It controls the distributed dc-ac converter as a VSM-based interface (VSM), and includes the following:

The digital simulation platforms that use mathematical models of the target systems may not be reliable because some components are usually inaccurate or unavailable. The hardware or field tests eliminate the problems of digital simulation platforms. However, it requires a long setup time, high cost, and application-specific design. These challenges obstruct the extensive utilization of the hardware or field test platforms. These platforms are costly to maintain and difficult to reconfigure. They limit the possibility of conducting the study of the different microgrid scenarios.

To solve these issues, aCHIL platform has been developed based on the OPAL-RT real-time simulators (OP5600/OP5607) and dSPACE MicroLabBox controller (ML1202). The CHIL platform combines the advantages of digital simulation and an external controller. The OP5600 real-time digital simulator at Clean Energy Research Lab in Nanyang Technological University is installed with 12 Intel Xeon E5 processors with a frequency of 3.2 GHz.

With rising global energy demand, transmission lines are operated at their limits, causing electrical gridsto operate under extreme voltage instability conditions. To meet the increased load-demand and the forced tendency across the globe of tilting towards even more renewable generation, solar and windfarms are integrated with increased size and capacity. These uncontrolled natural power injection againmay affect the system’s voltage stability. To avoid blackouts and to achieve the maximum voltagestability of power systems, operators need to do effective real-time grid monitoring and control at loadterminals. Load models are important in the analysis of voltage stability, and accurate load models areuseful in analysing the voltage stability conditions. Phasor-measurement-unit (PMU) based wide-areamonitoring and smart-automation is an innovative technology for measuring load voltage magnitude,phase angle, and frequency variations in a DFIG integrated large wind power system. This researchpaper focuses on estimating the real-time voltage stability through the use of linear, nonlinear, anddynamic load models in presence of a DFIG based wind-farm in WSCC three-machine nine-bus powernetwork using PMU data. This study is carried out using MATLAB-Simulink software.

This course introduces OPAL-RT systems and applications using RT-LAB. This course is a prerequisite for eMEGASIM, eFPGASIM, and ePHASORSIM. RT-LAB is used in a variety of domains, including power systems, power electronics, automotive applications, aerospace, mechatronics and more.

Prerequisites:

• Basic knowledge of Matlab®/Simulink®

Goals:

• Learn the fundamentals of real-time simulation

• Get started with RT-LAB Software

• Understand when and how to use distributed and parallel real-time simulation

• Connect models with I/Os

SECTION 1 – FROM OFFLINE SIMULATION TO REAL-TIME

• Video 1 – Startup (Preview)

• Video 2 – Creating a Model (Preview)

• Video 3a – Subsystems

• Video 3b – Communication Between Subsystems

• Video 3c – Maximizing Parallel Execution

• Video 3d – Hands-On1: Preparing a Simulink Model for Real-Time Simulation

• Video 4 – Simulation Parameters

SECTION 2 – USING THE SIMULATOR

• Video 5 – Running a Simulation in RT-LAB

• Video 6 – Execution Performance

• Video 7 – Probe Control

• Video 8 – Parameters, Variables & Signals

• Video 9 – Data Logging

• Video 10 – Inputs & Outputs

SECTION 3 – CUSTOMER SATISFACTION SURVEY

• Customer Satisfaction Survey

This work develops Hardware-in-the-loop (HIL) simulation against cyber attacks. The test setup in Opal-EXata cyber attack example ( paper), is based on the software-in-the-loop (CSIL) MGC, however, the hardware-in-the-loop HIL testing is left for the developer. Thus, we design a light-weight intelligent electronic device (IED) that performs MGC, interfaces are developed based on IEC 61850 GOOSE protocol from/to the real-time simulation and the MGC. They are executed on two equipment stages, FPGA and BeagleBoneBlack. The concept behind using these boards is based on their low cost, flexibility, support for various interfaces/protocols, I/O pins, and ease of configuration. CSIL versus CHIL tests are used to evaluate the MG behavior against different cyber attacks. We also evaluate the MGC designed control function in accordance with IEC 61850 GOOSE protocol. Two scenarios was carried out, In the first scenario, the MG will be islanded in second 1, in this case the MGC will check the power balance and implement the power balance operation emergency condition (the difference not exceeds 3MW). If the check emergency condition becomes true, the MGC attempts to immediately disconnect the sheddable Load 4 to maintain the MG stability. Be that as a delay attack is introduced to the GOOSE trip command packets sent from the MGC to Load 4, the load shedding function may fail to operate in the required timeframe. In this case this will cause severe unbalance between generation/load relationship and oscillations on MG nominal operation parameters such as e.g., frequency, voltages etc. Through the C code available delay function within the MGC initial code, a one-second delay attack is applied to the MGC GOOSE message command. MGC based on its normal operation will receive measurements that is sent from each MG assists via GOOSE. Be that as a Man-in-the-middle attack is introduced to the load measurements data. Before the load measurements data being received by MGC. The data is manipulated in the middle of its way to the MGC. In this case, the MGC may take incorrect actions based on these received non-critical measurements. According to the test scenario 2, the active power measurement from Load 2 is duplicated by applying a packet manipulation attack to the GOOSE message. In this case, the MGC will take the incorrect action (false tripping) because it perceives the controlling operation emergency condition is true (total load will be more than 3MW greater than the total generation). As a result, a trip command is sent to disconnect Load 3. . It also causes oscillations on MG nominal operation parameters such as e.g., frequency, voltages etc. Comparison between both achieving testing results, SIL and HIL will be made within the rest of this work. The results are The development and performance of an MGC against cyber attack control schemes have been implemented in this paper. These are done by design and deployed on a light-weighted intelligent IED. The MGC control solution and its relevant communication system have been designed in compliance with the IEC 61850 and executed on two equipment stages, FPGA and BeagleBoneBlack. CSIL versus CHIL tests are used to evaluate/assess the MG behavior against different cyber attack scenarios. Moreover, we also evaluated IEC 61850 GOOSE protocol implementation, processing and finally control action performance. The obtained results demonstrate that the light-weight MGC approach and data modeling of various IEC 61850 predefined data object LNs are correct for the design of the power balance control/protection function against cyber attack. In addition, they demonstrate the successful implementations of the designed control/protection function and the modeled MGC LNs in various cyber-attack case studies on reliable detection of the emergency condition. Further work on the analysis of the data received by MGC, implementation of different cyber attacks and power balance detection algorithms is needed.

When HYPERSIM’s in-schematic signal monitoring is not enough, when networks are very large, or when more types of widgets are required, or even for training purposes, it may be practical to build distinct dashboards with a more concise organization of the information. Several tools can be used to achieve this, such as NI LabVIEW. Information is sent in real time from HYPERSIM using compatible communication protocols such as TCP/UDP or OPC UA and displays are refreshed every few milliseconds.

Jean Patric da Costa was born in Santa Maria, Brazil, in 1979. He received a B.S. degree in electrical engineering and a master’s and Ph.D. degrees from the Federal University of Santa Maria, Santa Maria, Brazil, in 2004, 2006, and 2011. He is currently a Professor with the Department of Electrical Engineering, Universidade Tecnológica Federal do Paraná (UTFPR), Curitiba, Brazil. His research interests include control of static converters, smart grids, ancillary services, and distributed generators.

Philippe Viarouge was born in Périgueux France in 1954. He received the engineering and Doctor of engineering degrees, the french accreditation to supervise research (HDR) from the “Institut National Polytechnique de Toulouse”, France, in 1976, 1979 and 1992.

Since 1979, he has been a professor with the Department of Electrical & Computer Engineering at Laval University, Quebec, Canada. He is working in the research laboratory LEEPCI. His research interests include the design & modeling of electrical machines and medium frequency magnetic components, AC drives and power electronics. He was Project Associate and consulting engineer at CERN, Geneva, Switzerland, in 2010 and 2018 respectively.

In order to access this page, please sign in below.